Περίληψη

Η οικογένεια Virtex της Xilinx, περιλαμβάνει μια σειρά από FPGAs σχεδιασμένα να προσφέρουν υψηλή απόδοση

και χωρητικότητα. Αποτελούν μία από τις πλέον επιτυχημένες και διαδεδομένες οικογένειες FPGAs. Στο παρόν

άρθρο θα παρουσιαστούν αναλυτικά τα χαρακτηριστικά τους όσον αφορά την λειτουργικότητα, την αρχιτεκτονική

και τον τρόπο προγραμματισμού τους.

Προαπαιτούμενα

Για την κατανόηση του άρθρου αυτού, ο αναγνώστης πρέπει να διαθέτει βασικές γνώσεις σε έννοιες

σχετικές με VLSI (Very Large

Scale Ιntegration), FPGAs (Field Programmable Gate Arrays) και γενικότερα σχεδίασης ψηφιακών συστημάτων. Εφόσον

υπάρχει κάποιο σχετικό υπόβαθρο, ο βαθμός δυσκολίας του άρθρου είναι περιορισμένος.

Γενικά Χαρακτηριστικά

Η οικογένεια ολοκληρωμένων Virtex είναι μια σειρά από FPGAs σχεδιασμένα να προσφέρουν υψηλή

απόδοση και χωρητικότητα. Η πυκνότητα τους ανέρχεται σε 50k μέχρι 1Μ ισοδύναμες λογικές πύλες, ενώ

έχουν δυνατότητα να λειτουργήσουν σε ταχύτητες μέχρι και 200ΜHz.

Η διαμόρφωση των ολοκληρωμένων αυτών βασίζεται σε SRAM, καθιστώντας δυνατό τον απεριόριστο αριθμό

επαναπρογραμματισμών τους. Παράλληλα προσφέρονται πολλαπλοί τρόποι για τον προγραμματισμό, αυξάνοντας

την ευελιξία τους.

Η επικοινωνία με εξωτερικά κυκλώματα γίνεται μέσω ενός interface (SelectIO) που υποστηρίζει μια

πληθώρα διαφορετικών προτύπων υψηλής απόδοσης. Ενσωματωμένα βρίσκονται και τα κυκλώματα για το ρολόι

και την διαχείριση του. Τα τελευταία αποτελούνται από δίκτυα διανομής καθολικού ρολογιού χαμηλής

καθυστέρησης, από δίκτυα τοπικών ρολογιών και από αφοσιωμένα κυκλώματα για τον έλεγχο του ρολογιού

(delay-locked loops - DLLs).

Οι συσκευές αυτές περιλαμβάνουν ένα ιεραρχικό σύστημα μνήμης. Look - up πίνακες μπορούν να

διαμορφωθούν ώστε να χρησιμοποιηθούν ως 16-bit RAM, 32-bit RAM, 16-bit dual-ported RAM ή 16-bit

Καταχωρητής Ολίσθησης. Επίσης διατίθενται προγραμματιζόμενες σύγχρονες dual-ported 4k-bits RAMs,

ενώ υπάρχουν και interfaces για εξωτερικές μνήμες υψηλής απόδοσης.

Η αρχιτεκτονική τους είναι τέτοια ώστε να επιτυγχάνεται μια ισορροπία ανάμεσα στα δύο

χαρακτηριστικά της απόδοσης και της χωρητικότητας. Έτσι διαθέτουν αφοσιωμένη λογική κρατουμένου για

αριθμητική υψηλής ταχύτητας, καθώς επίσης και εγγενή υποστήριξη για πολλαπλασιαστές. Υπάρχουν

άφθονοι καταχωρητές/μανταλωτές με επίτρεψη ρολογιού και διπλό σύγχρονο / ασύγχρονο set και reset.

Περιλαμβάνεται τέλος στα ολοκληρωμένα εσωτερική λογική για την υποστήριξη του IEEE 1149.1 boundary

scan και θερμοδίοδοι για την θερμοκρασία.

Η οικογένεια Virtex είναι κατασκευασμένη σε 0.22μm CMOS διαδικασία με 5 στρώσεις μετάλλου. Τάση

λειτουργίας είναι τα 2.5 Volts.

Περιγραφή Αρχιτεκτονικής

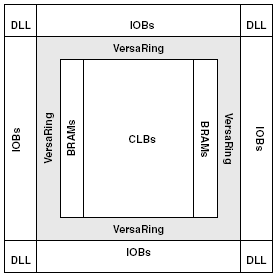

Όπως φαίνεται από το σχήμα που ακολουθεί (Σχήμα 1), το Virtex αποτελείται από δύο βασικά

προγραμματιζόμενα στοιχεία : τα προγραμματιζόμενα μπλοκ λογικής (Configurable Logic Blocks - CLBs)

και τα μπλοκ εισόδου / εξόδου (Input / Output Blocks - IOBs). Τα πρώτα παρέχουν τα λειτουργικά

εκείνα στοιχεία που απαιτούνται για την κατασκευή λογικής και τα δεύτερα παρέχουν την διασύνδεση

μεταξύ των ακροδεκτών του ολοκληρωμένου και των CLBs.

Σχήμα 1. Επισκόπηση Αρχιτεκτονικής Virtex

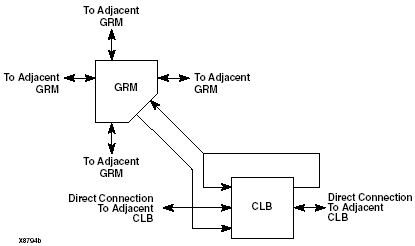

Tα CLBs διασυνδέονται μέσω ενός γενικού πίνακα δρομολόγησης (General Routing Matrix - GRM). Ο GRM

αποτελείται από ένα διάνυσμα από διακόπτες δρομολόγησης που τοποθετούνται στις διασταυρώσεις των

οριζόντιων και καθέτων καναλιών δρομολόγησης. Κάθε CLB τοποθετείται μέσα σε ένα VersaBlock που

επίσης παρέχει τοπικούς πόρους δρομολόγησης για την σύνδεση του CLB με το GRM.

Το VersaRing interface εισόδου / εξόδου προσφέρει επιπλέον πόρους δρομολόγησης γύρω από την

περιφέρεια της συσκευής. Αυτή η δρομολόγηση βελτιώνει την διασύνδεση με τις εισόδους / εξόδους και

διευκολύνει την ανάθεση των ακροδεκτών.

Πέρα από τα προαναφερθέντα, στο GRM συνδέονται και μια σειρά από άλλα κυκλώματα.

- Αφοσιωμένα μπλοκ μνήμης των 4096 bits το καθένα

- DLLs ρολογιού, για την αναπλήρωση της καθυστέρησης διάδοσης του ρολογιού και για τον έλεγχο περιοχής ρολογιού

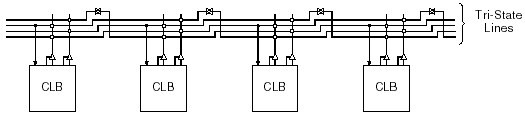

- Buffers τριών καταστάσεων (BUFTs) που σχετίζονται με κάθε CLB που οδηγεί αφοσιωμένους οριζόντιους πόρους δρομολόγησης

Τιμές που αποθηκεύονται σε κελιά στατικής μνήμης ελέγχουν τα προγραμματιζόμενα λογικά στοιχεία και τους διασυνδετικούς πόρους.

Οι τιμές αυτές φορτώνονται στα κελιά της μνήμης κατά την διαδικασία ενεργοποίησης της συσκευής (power-up) και υπάρχει η δυνατότητα να ξαναφορτωθούν εάν είναι απαραίτητο να αλλάξει η λειτουργία της συσκευής.

Μπλοκ Εισόδου / Εξόδου

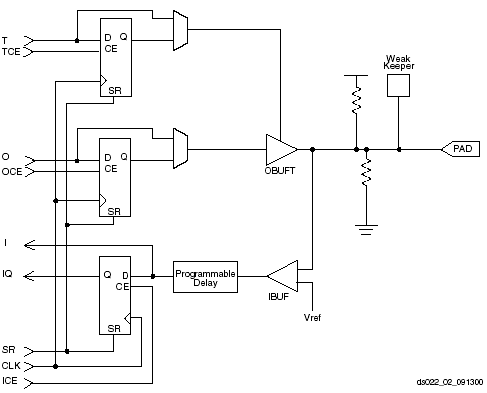

Ένα Virtex ΙΟΒ (δείτε το Σχήμα 2) περιλαμβάνει SelectIO εισόδους και εξόδους που υποστηρίζουν μια

μεγάλη ποικιλία από πρότυπα σηματοδοσίας εισόδου / εξόδου.

Σχήμα 2. Virtex Input/Output Block (IOB)

Tα τρία ΙΟΒ αποθηκευτικά στοιχεία λειτουργούν είτε σαν ακμοπυροδότητα τύπου D flip-flops, είτε ως

μανταλωτές ευαίσθητους σε στάθμη. Κάθε ΙΟΒ έχει ένα σήμα ρολογιού που μοιράζεται στα τρία flip-flops

και ανεξάρτητο clock enable για κάθε flip-flop.

Επιπρόσθετα των δύο αυτών σημάτων (CLK και CE), τα τρία flip-flops μοιράζονται και ένα Set / Reset

(SR) σήμα. Για κάθε flip-flop, αυτό το σήμα μπορεί να διαμορφωθεί ανεξάρτητα σαν σύγχρονο Set,

ασύγχρονο Reset, ασύγχρονο Preset ή ασύγχρονο Clear.

Σε κάθε ακροδέκτη είναι προσαρτημένες προαιρετικές pull-up και pull-down αντιστάσεις. Πριν από

την διαμόρφωση του Virtex, όλοι οι ακροδέκτες που δεν πρόκειται να χρησιμοποιηθούν οδηγούνται σε

υψηλή εμπέδηση, ενώ οι pull-down αντιστάσεις είναι απενεργοποιημένες. Οι είσοδοι μπορεί να είναι

προαιρετικά pulled-up. Η ενεργοποίηση των pull - up αντιστάσεων πριν από την διαμόρφωση ελέγχεται σε

καθολική βάση από τους ακροδέκτες τύπου διαμόρφωσης (configuration mode pins). Εάν οι pull-up

αντιστάσεις δεν ενεργοποιηθούν, τότε πρέπει εξωτερικές pull-up ή pull-down αντιστάσεις να παρέχονται

στoυς ακροδέκτες που είναι ανάγκη να βρίσκονται σε καλά ορισμένη στάθμη, καθώς στην περίπτωση αυτή

οι ακροδέκτες θα μπορούν να πάρουν απροσδιόριστες τιμές (float).

Μονοπάτια Εισόδου / Εξόδου

Ένας buffer στο μονοπάτι εισόδου του Virtex ΙΟΒ, δρομολογεί το σήμα εισόδου είτε απευθείας στην

εσωτερική λογική, είτε διαμέσου ενός flip-flop εισόδου.

Ένα προαιρετικό στοιχείο καθυστέρησης στην είσοδο D αυτού του flip-flop χρησιμοποιείται για να

εξαλείψει τον hold χρόνο από ακροδέκτη σε ακροδέκτη. Η καθυστέρηση είναι σε συγχρονισμό με την

εσωτερική καθυστέρηση διάδοσης του ρολογιού του FPGA και έτσι όταν χρησιμοποιείται εξασφαλίζει ότι ο

χρόνος hold από ακροδέκτη σε ακροδέκτη είναι μηδενικός.

Το μονοπάτι εξόδου περιλαμβάνει έναν buffer εξόδου τριών καταστάσεων που οδηγεί το σήμα εξόδου

στον ακροδέκτη. Όπως και στην περίπτωση του μονοπατιού εισόδου, το σήμα αυτό μπορεί να οδηγηθεί από

την εσωτερική λογική είτε κατευθείαν στον buffer είτε μέσω ενός προαιρετικού flip-flop εξόδου.

Ο έλεγχος τριών καταστάσεων της εξόδου μπορεί επίσης να δρομολογηθεί κατευθείαν από την εσωτερική

λογική ή μέσω ενός flip-flop που παρέχει σύγχρονη ενεργοποίηση / απενεργοποίηση.

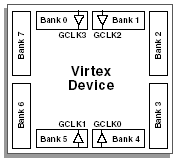

I/O Banking

Όπως έχει ήδη αναφερθεί, το Virtex υποστηρίζει μια σειρά από πρότυπα εισόδου / εξόδου. Για να τα

υποστηρίξει αυτά, πρέπει να παρέχονται εξωτερικά οι απαιτούμενες τάσεις αναφοράς εισόδου (Input

Reference Voltage - VREF) και εξόδου (Output Source Voltage - VCCO). Οι τάσεις αυτές συνδέονται σε

ακροδέκτες της συσκευής που εξυπηρετούν ομάδες από IOBs, που ονομάζονται banks. Έτσι προκύπτουν

κάποιοι περιορισμοί που καθορίζουν ποια πρότυπα εισόδου / εξόδου μπορούν να συνδυαστούν σε μια

δοσμένη bank.

Σχήμα 3. Virtex I/O Banks

Κάθε πλευρά του FPGA χωρίζεται σε δύο banks. Με τον τρόπο αυτό, μπορούν να υπάρξουν 8 διαφορετικές

banks (Σχήμα 3). Κάθε bank έχει πολλαπλoύς VCCO ακροδέκτες, που πρέπει να συνδέονται στην ίδια

τάση. Η τάση αυτή καθορίζεται από τα πρότυπα εισόδου / εξόδου που χρησιμοποιού-νται. Σε κάθε bank,

μπορούν να χρησιμοποιηθούν περισσότερα του ενός πρότυπα, αρκεί για αυτά να απαιτείται το ίδιο

VCCO. Στον σχετικό πίνακα που παρατίθεται (Πίνακας 1) παρουσιάζονται τα διάφορα συμβατά πρότυπα.

Από την άλλη, για τα διάφορα πρότυπα εισόδου που μπορούν να χρησιμοποιηθούν, πρέπει ανάλογα με

την περίπτωση να δοθεί κάποια εξωτερική τάση κατωφλίου (VREF). Οι VREF

ακροδέκτες μιας bank διασυνδέονται εσωτερικά, με συνέπεια μόνο μία VREF τάση να μπορεί να

χρησιμοποιηθεί σε κάθε bank.

Πίνακας 1. Συμβατά Πρότυπα Εξόδου

| VCCO |

Συμβατά Πρότυπα |

| 3.3V |

PCI, LVTTL, SSTL3 I, SSTL3 II, CTT, AGP, GTL, GTL |

| 2.5V |

SSTL2 I, SSTL2 II, LVCMOS2, GTL, GTL+ |

| 1.5V |

HSTL I, HSTL III, HSTL IV, GTL, GTL+ |

Προγραμματιζόμενα Λογικά Μπλοκ

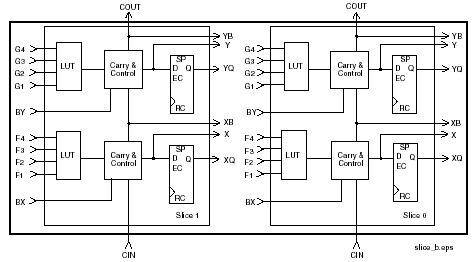

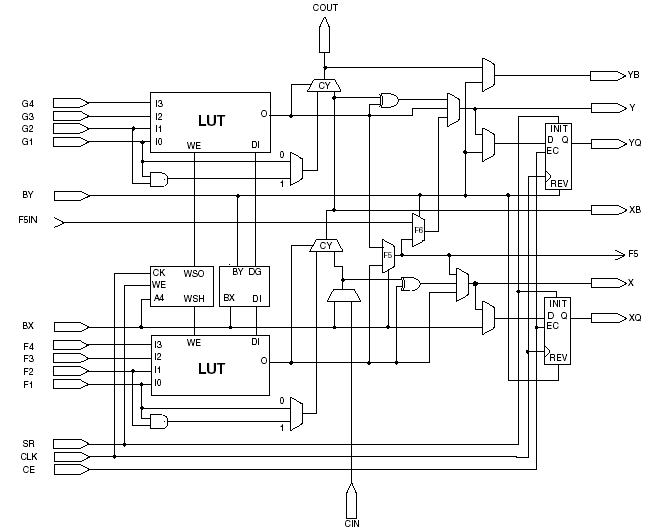

Το βασικό δομικό μπλοκ ενός Virtex CLB είναι το λογικό κελί (logic cell - LC). Ένα LC περιλαμβάνει

μία τεσσάρων εισόδων γεννήτρια συναρτήσεων, λογική κρατουμένου, και ένα αποθηκευτικό στοιχείο. Η

έξοδος από την γεννήτρια συναρτήσεων οδηγεί τόσο την έξοδο του CLB όσο και την D είσοδο του

flip-flop. Κάθε CLB περιέχει τέσσερα LCs, οργανωμένα σε δύο όμοια κομμάτια (slices).

Στο Σχήμα 4 παρουσιάζεται ένα CLB με τα δύο του κομμάτια. Στο επόμενο σχήμα (Σχήμα 5) δίνεται

μια λεπτομερής εικόνα ενός κομματιού του CLB.

Σχήμα 4. 2-Slice Virtex CLB

Πέρα από τα τέσσερα βασικά LCs, το CLB περιέχει λογική που συνδυάζει γεννήτριες συναρτήσεων για

να παρέχει συναρτήσεις πέντε ή έξι εισόδων. Συνεπώς, όταν εκτιμάται ο αριθμός των πυλών συστήματος

που παρέχει κάθε συσκευή, κάθε CLB μετράει ως 4.5 LCs.

Σχήμα 5. Λεπτομερής Άποψη ενός Virtex Slice

I/O Banking

Σε κάθε slice υπάρχει επιπλέον λογική που επιτρέπει την υλοποίηση συναρτήσεων περισσότερων

εισόδων. Έτσι ο πολυπλέκτης που συνδέει τις γεννήτριες συναρτήσεων προσφέρει την δυνατότητα να

υλοποιηθεί οποιαδήποτε συνάρτηση 5 εισόδων, ένας 4 - σε - 1 πολυπλέκτης ή επιλεγμένες συναρτήσεις

μέχρι 9 εισόδων.

Επιπλέον υπάρχει ένας πολυπλέκτης που συνδέει τις εξόδους και των τεσσάρων γεννητριών συναρτήσεων

του CLB. Είναι επιτρεπτή έτσι η υλοποίηση οποιασδήποτε συνάρτησης 6 εισόδων, ή ενός πολυπλέκτη 8-σε-1

ή επιλεγμένων συναρτήσεων μέχρι και 19 εισόδων.

Αριθμητική Λογική

Αφοσιωμένη λογική για κρατούμενο παρέχει γρήγορη αριθμητική κρατουμένου για την υλοποίηση

ταχύτατων αριθμητικών συναρτήσεων. Επίσης η αριθμητική λογική περιλαμβάνει μια XOR πύλη που

επιτρέπει την υλοποίηση ενός πλήρη αθροιστή του ενός bit σε κάθε LC. Μια πύλη AND, τέλος, αφιερωμένη

αποκλειστικά για αριθμητικές πράξεις βελτιώνει την υλοποίηση πολλαπλασιαστών.

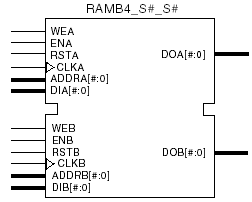

Block SelectRAM

Τα FPGAs της σειράς Virtex, ενσωματώνουν αρκετά μεγάλα μπλοκ από SelectRAM μνήμες. Αυτά

συμπληρώνουν τις κατανεμημένες LUT SelectRAMs που προσφέρουν ρηχές δομές RAM μνήμης υλοποιημένης στα

CLBs.

Τα Block SelectRAM τμήματα μνήμης είναι οργανωμένα σε στήλες. Όλες οι συσκευές της οικογένειας

Virtex περιέχουν δύο τέτοιες στήλες, μία κατά μήκος κάθε κάθετης πλευράς. Οι στήλες αυτές εκτείνονται

στο πλήρες ύψος του ολοκληρωμένου. Κάθε τμήμα μνήμης έχει ύψος ίσο με 4 CLB.

Κάθε κελί ενός μπλοκ SelectRAM (Σχήμα 6), είναι μια πλήρως σύγχρονη dual-ported RAM 4096-bit, με

ανεξάρτητα σήματα ελέγχου για κάθε port. Το πλάτος των δεδομένων κάθε port μπορεί να διαμορφωθεί

ανεξάρτητα, παρέχοντας έτσι ενσωματωμένες μετατροπές στο πλάτος του διαύλου.

Σχήμα 6. Dual-Port Block SelectRAM

Προγραμματιζόμενος Πίνακας Δρομολόγησης

Τοπική Δρομολόγηση

Το VersaBlock παρέχει πόρους τοπικής δρομολόγησης (Σχήμα 7) προσφέροντας τους ακόλουθους τρεις

τύπους συνδέσεων :

- Συνδέσεις μεταξύ των LUTs, των flip-flops και του GRM (General Routing Matrix)

- Εσωτερικά στα CLB μονοπάτια ανατροφοδότησης που παρέχουν υψηλής ταχύτητας συνδέσεις σε LUTs του ίδιου CLB, ενώνοντας τα με ελάχιστη καθυστέρηση δρομολόγησης

- Απευθείας μονοπάτια που παρέχουν συνδέσεις υψηλής ταχύτητας μεταξύ γειτονικών (κατά τον οριζόντιο άξονα) CLBs, εξαλείφοντας την καθυστέρηση του GRM

Σχήμα 7. Τοπική Δρομολόγηση του Virtex

Δρομολόγηση Γενικού Σκοπού

Η πλειοψηφία των πόρων διασύνδεσης σχετίζονται με αυτό το επίπεδο της ιεραρχίας δρομολόγησης. Οι

πόροι αυτοί βρίσκονται τοποθετημένοι σε οριζόντια και κάθετα κανάλια που σχετίζονται με τις γραμμές

και τις στήλες των CLBs.

Δίπλα σε κάθε CLB υπάρχει ένας γενικός πίνακας δρομολόγησης (General Routing Matrix - GRM). Ο GRM

είναι ένας πίνακας από διακόπτες μέσω του οποίου συνδέονται οριζόντιοι και κατακόρυφοι πόροι

δρομολόγησης, και είναι το μέσο που δίνει στο CLB πρόσβαση στο δίκτυο δρομολόγησης γενικού σκοπού.

Γραμμές μονού - μήκους δρομολογούν GRM σήματα σε γειτονικά GRMs σε καθεμία από τις τέσσερις

κατευθύνσεις. Επίσης υπάρχει και ένας αριθμός από Hex γραμμές, οι οποίες δρομολογούν GRM σήματα σε

άλλα GRM που βρίσκονται έξι μπλοκ μακριά σε καθεμία από τις τέσσερις κατευθύνσεις. Οι γραμμές αυτές

μπορούν να οδηγηθούν μόνο από τα άκρα τους και πρόσβαση σε αυτές μπορούν να έχουν τα στοιχεία που

βρίσκονται είτε στα άκρα τους είτε στο μέσο τους (δηλαδή τρία μπλοκ από την πηγή). Το ένα τρίτο των

γραμμών αυτών είναι διπλής κατεύθυνσης, ενώ οι υπόλοιπες είναι μονοκατευθυντικές.

Τέλος, διατίθενται και γραμμές μεγάλου μήκους που χρησιμοποιούνται για την αποτελεσματική και

γρήγορη διανομή σημάτων κατά μήκος της συσκευής.

Δρομολόγηση Εισόδου / Εξόδου

Οι συσκευές της οικογένειας Virtex διαθέτουν επιπλέον διασυνδετικούς πόρους κατά μήκος της

περιφέρειας τους, που σχηματίζουν ένα interface μεταξύ των CLBs και των IOBs (VersaRing).

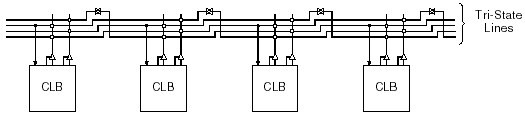

Αφοσιωμένη Δρομολόγηση

Λόγω των ιδιαίτερων απαιτήσεων που έχουν, η Virtex αρχιτεκτονική προσφέρει αφοσιωμένες γραμμές

σε δύο κλάσεις σημάτων :

- Για διαύλους τριών καταστάσεων πάνω στο ολοκληρωμένο παρέχονται οριζόντιοι πόροι

δρομολόγησης. Τέσσερις διαχωρίσιμες γραμμές διαύλου παρέχονται σε κάθε σειρά από CLB, επιτρέποντας

έτσι την ύπαρξη πολλαπλών διαύλων σε κάθε γραμμή (Σχήμα 8).

- Δύο δίκτυα ανά CLB προωθούν σήματα κρατουμένου κάθετα στο γειτονικό CLB.

Σχήμα 8. BUFT Συνδέσεις σε Αφιερωμένες Οριζόντιες Γραμμές Διαύλου

Καθολική Δρομολόγηση

Οι πόροι αυτοί χρησιμοποιούνται για να διανείμουν σήματα ρολογιού και σήματα με πολύ μεγάλο

fanout κατά μήκος της συσκευής. Είναι δύο ειδών : οι κύριοι καθολικοί πόροι δρομολόγησης και οι

δευτερεύοντες τοπικού ρολογιού πόροι. Οι κύριοι καθολικοί πόροι δρομολόγησης αποτελούνται από

τέσσερα δίκτυα συνδεδεμένα σε συγκεκριμένους ακροδέκτες και χρησιμοποιούνται για να διανείμουν

σήματα ρολογιού μεγάλου fanout με ελάχιστο skew. Το δευτερεύον τοπικό δίκτυο ρολογιού αποτελείται

από έναν αριθμό γραμμών και παρουσιάζει μεγάλη ευελιξία καθότι δεν περιορίζεται στην δρομολόγηση

σημάτων από τους ακροδέκτες ρολογιού.

Configuration

Τα FPGA της οικογένειας Virtex μπορούν να προγραμματιστούν φορτώνοντας την configuration πληροφορία

στην εσωτερική configuration μνήμη. Προσφέρονται τέσσερις διαφορετικοί τρόποι configuration : master

serial, slave serial, SelectMAP και Boundary Scan. Το σύνολο των configuration bits ονομάζεται

configuration bitstream και αποτελείται από σειρά εντολών και δεδομένων configuration. H εγγραφή

μέρους ή ολόκληρου του configuration γίνεται με την παράθεση configuration εντολών προς το σχετικό

interface ακολουθούμενες από τα αντίστοιχα configuration δεδομένα.

Το SelectMAP interface είναι ένα 8-bit interface με την συσκευή. Σε κάθε κύκλο γράφεται μια οκτάδα

από το configuration bitstream. Αντίθετα τα υπόλοιπα interfaces είναι σειριακά, δηλαδή σε κάθε κύκλο

γράφεται 1 bit από το configuration bitstream.

Το configuration της συσκευής γίνεται μέσω ενός αριθμού ακροδεκτών. Από αυτούς άλλοι προορίζονται

αποκλειστικά για την συγκεκριμένη χρήση και άλλοι μετά το πέρας της διαδικασίας μπορούν να

χρησιμοποιηθούν από τον χρήστη.

Πέρα από την εγγραφή της configuration πληροφορίας στην συσκευή, υπάρχει η δυνατότητα να διαβαστούν

πίσω τα δεδομένα που είναι αποθηκευμένα στην configuration μνήμη. Από τα παραπάνω interfaces για την

συγκεκριμένη λειτουργία μπορούν να χρησιμοποιηθούν μόνο τα SelectMAP και Boundary Scan. Κατά την

ανάγνωση της configuration πληροφορίας χρησιμοποιούνται προφανώς οι ίδιοι ακροδέκτες επιτελώντας τις

αντίστοιχες λειτουργίες.

Configuration Στήλες

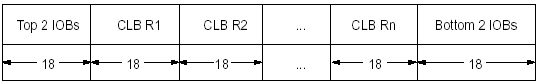

Η configuration μνήμη μπορεί να ειδωθεί σαν ένας τετραγωνικός πίνακας από bits. Τα bits αυτά

ομαδοποιούνται σε κάθετα πλαίσια πλάτους ενός bit εκτεινόμενα από την κορυφή του πίνακα μέχρι το

κατώτερο σημείο του. Ένα πλαίσιο είναι η ατομική μονάδα του configuration - είναι δηλαδή το μικρότερο

κομμάτι της configuration μνήμης που μπορεί να γραφεί ή να διαβαστεί.

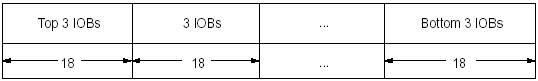

Τα πλαίσια ομαδοποιούνται σε μεγαλύτερες μονάδες που καλούνται στήλες. Υπάρχουν διάφοροι τύποι

στηλών. Κάθε συσκευή περιέχει μια κεντρική στήλη που περιλαμβάνει το configuration για τους τέσσερις

ακροδέκτες καθολικού ρολογιού. Δύο IOB στήλες συγκεντρώνουν όλη την configuration πληροφορία για όλα

τα IOBs που είναι τοποθετημένα στο αριστερό και δεξί άκρο της συσκευής. Η πλειοψηφία των στηλών είναι

CLB στήλες. Κάθε μία από αυτές περιέχει την configuration πληροφορία που σχετίζεται με κάθε στήλη από

CLB και τα δύο IOBs πάνω και κάτω από την στήλη αυτή.

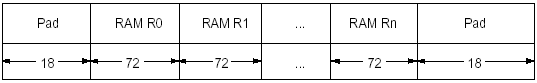

Εκτός από τους παραπάνω τύπους στηλών, υπάρχουν και άλλοι δύο που σχετίζονται με την block RAM. Ο

πρώτος καθορίζει το περιεχόμενο της και ο δεύτερος την διασύνδεση της.

Στο σχήμα που ακολουθεί (Σχήμα 9) δίνονται οι στήλες για μια Virtex συσκευή :

Σχήμα 9. Παράδειγμα Configuration Στηλών

Configuration Διευθυνσιοδότηση

Όλος ο χώρος διευθύνσεων χωρίζεται σε τύπους μπλοκ. Υπάρχουν δύο τύποι μπλοκ : RAM και CLB. Ο τύπος

RAM περιέχει μόνο τις στήλες περιεχομένου της block SelectRAM (όχι τις στήλες που σχετίζονται με την

διασύνδεση). Ο τύπος CLB περιέχει όλους τους υπόλοιπους τύπους στηλών.

Και οι δύο αυτοί χώροι διευθύνσεων υποδιαιρούνται σε μείζονες (major) και ελάσσονες (minor)

διευθύνσεις. Κάθε configuration στήλη έχει μια μοναδική major διεύθυνση μέσα στον RAM ή CLB χώρο. Κάθε

configuration πλαίσιο έχει μια μοναδική minor διεύθυνση μέσα στην στήλη.

Πλαίσιο

Τα πλαίσια γράφονται και διαβάζονται σειριακά με αυξανόμενες διευθύν-σεις για κάθε λειτουργία.

Πολλαπλά συνεχόμενα πλαίσια μπορούν να διαβαστούν ή να γραφούν με μία μοναδική configuration εντολή.

Το μικρότερο ποσό δεδομένων που μπορούν να γραφούν ή να διαβαστούν με μια μόνο εντολή είναι ένα

πλαίσιο. Ολόκληρο το CLB διάνυσμα με τα IOBs και την block SelectRAM διασύνδεση μπορούν να διαβαστούν

ή να γραφούν με μια μοναδική configuration εντολή.

Το μέγεθος ενός πλαισίου εξαρτάται από τον αριθμό των γραμμών της συσκευής. Ο αριθμός των

configuration bits σε ένα πλαίσιο προσδιορίζεται από την σχέση 18 x (# CLB_γραμμές + 2) και

προστίθενται μηδενικά στο τέλος για να χωρά σε λέξεις των 32-bits.

Κάθε πλαίσιο απλώνεται κάθετα στην συσκευή, με την αρχή του πλαισίου να αντιστοιχίζεται στην

κορυφή της συσκευής. Θεωρώντας το όμως σαν μέρος του configuration bitstream, είναι πιο εύκολο να

ειδωθεί σαν οριζόντιο, με το πιο αριστερό τμήμα του να αντιστοιχίζεται στην κορυφή της συσκευής. Έτσι

στα σχήματα που ακολουθούν , φαίνονται τα περιεχόμενα ενός frame για κάθε έναν από τους τύπους στηλών

που υπάρχουν. Στα σχήματα αυτά ο αριθμός κάτω από κάθε στοιχείο της συσκευής υποδηλώνει τον αριθμό των

configuration bits που αντιστοιχούν στο στοιχείο αυτό.

Τα bits κάθε πλαισίου ομαδοποιούνται σε λέξεις των 32-bits. Έτσι αν σε κάποιο από τα πλαίσια ο

αριθμός των απαιτούμενων bits είναι μικρότερος, τότε στο τέλος συμπληρώνονται με μηδενικά, ώστε ο

συνολικός αριθμός των bits του πλαισίου να είναι ακέραιο πολλαπλάσιο του 32. Εξαίρεση αποτελούν τα

πλαίσια για τις στήλες περιεχομένου της block SelectRAM. Στα πλαίσια αυτά τόσο στην αρχή όσο και στο

τέλος υπάρχει ένας καθορισμένος αριθμός από μηδενικά. Και πάλι βέβαια ισχύει ότι αν ο συνολικός

αριθμός των bits δεν είναι ακέραιο πολ/σιο του 32, τότε στο τέλος θα προστεθούν κάποια έξτρα μηδενικά.

Σχήμα 10. Οργάνωση Πλαισίου Στήλης CLB

Σχήμα 11. Οργάνωση Πλαισίου Στήλης IOB

Σχήμα 12. Οργάνωση Πλαισίου Στήλης Περιεχομένου Block SelectRAM

Configuration Δεδομένα

Τα configuration δεδομένα είναι οργανωμένα σε λέξεις των 32-bits. Υπάρχουν δύο κύριες εντολές που

εμφανίζονται στα δεδομένα αυτά : η Ανάγνωση και η Εγγραφή. Μια configuration εντολή εκτελείται όταν η

configuration εντολή γράφεται ή διαβάζεται από τον σχετικό καταχωρητή εντολής.

Μια εντολή είναι οργανωμένη σαν ένα πακέτο με μια λέξη επικεφαλίδα και προαιρετικές λέξεις

δεδομένων. Η επικεφαλίδα είναι η πρώτη λέξη που γράφεται στον κατάλληλο καταχωρητή εντολής για μια

λειτουργία ανάγνωσης ή εγγραφής. Μια επικεφαλίδα περιέχει ένα πεδίο τύπου, ένα πεδίο εντέλων, ένα

πεδίο διεύθυνσης καταχωρητή και ένα πεδίο καταμετρητή λέξεων.

Το πεδίο διεύθυνσης καταχωρητή καθορίζει ποιος καταχωρητής είναι ο καταχωρητής στόχος της εντολής.

Το πεδίο καταμετρητή λέξεων περιέχει έναν ακέραιο αριθμό από 0 μέχρι 2,047. Ο αριθμός αυτός υποδεικνύει

τον αριθμό των λέξεων που ακολουθούν την επικεφαλίδα. Για να γίνει αναφορά σε μεγαλύτερους αριθμούς

λέξεων (ανάμεσα σε 2,048 και 1,048,575 λέξεις), χρησιμοποιείται μια λέξη ως επέκταση της επικεφαλίδας.

Configuration Δεδομένα

Η πρόσβαση στην configuration λογική και ο έλεγχος της γίνονται μέσω ενός συνόλου 32-bit καταχωρητών

που ονομάζονται configuration καταχωρητές. Μια συνοπτική εικόνα των καταχωρητών αυτών δίνει ο Πίνακας

2.

Πίνακας 2. Configuration Καταχωρητές

| Όνομα Καταχωρητή |

Μνημονικό |

R / W |

Δυαδική Διεύθυνση |

| CRC |

CRC |

R/W |

0000 |

| Frame Address |

FAR |

R/W |

0001 |

| Frame Data Input |

FDRI |

W |

0010 |

| Frame Data Output |

FDRO |

R |

0011 |

| Command |

CMD |

R/W |

0100 |

| Control |

CTL |

R/W |

0101 |

| Control Mask |

MASK |

R/W |

0110 |

| Status |

STAT |

R |

0111 |

| Legacy Output |

LOUT |

W |

1000 |

| Configuration Option |

COR |

R/W |

1001 |

| Reserved |

- |

- |

1010 |

| Frame Length |

FLR |

R/W |

1011 |

| Reserved |

- |

- |

1100 |

| Reserved |

- |

- |

1101 |

| Reserved |

- |

- |

1110 |

| Reserved |

- |

- |

1111 |

To περιεχόμενο του Kαταχωρητή Εντολής (Command Register - CMD) μεταφράζεται από την μηχανή

καταστάσεων του configuration. Οι εντολές αυτές ελέγχουν την λειτουργία της μηχανής καταστάσεων του

configuration, τον Καταχωρητή Δεδομένων Πλαισίου (Frame Data Register - FDR) και κάποια από τα

καθολικά σήματα. Η εντολή στον CMD εκτελείται κάθε φορά που ο FAR φορτώνεται με μια νέα τιμή.

Ο Καταχωρητής Επιλογών Configuration (COR) χρησιμοποιείται για να επιλεγούν διάφορες επιλογές του

configuration. Οι επιλογές αυτές σχετίζονται με τον χειρισμό configuration ακροδεκτών της συσκευής,

με την πηγή του ρολογιού κατά την διαδικασία του εκκίνησης, με τον προγραμματισμό ορισμένων ενεργειών

κατά την φάση της εκκίνησης κ.ά.

Ο καταχωρητής CRC (Cyclic Redundancy Check) χρησιμοποιείται για να επαληθευτεί η ορθότητα των

configuration δεδομένων. Όταν κάποια δεδομένα γράφονται σε έναν οποιοδήποτε καταχωρητή (εκτός από

τον LOUT) μια 16-bit CRC τιμή υπολογίζεται χρησιμοποιώντας τόσο τα δεδομένα του καταχωρητή όσο και

την διεύθυνση. Η τιμή αυτή αποθηκεύεται στον CRC καταχωρητή. Στο τέλος μιας σειράς από εγγραφές, μία

προϋπολογισμένη CRC τιμή για το μπλοκ γράφεται στον CRC καταχωρητή. Αν η τελική τιμή στον καταχωρητή

δεν είναι 0, τότε αυτό σηματοδοτεί την ύπαρξη σφάλματος και η configuration λογική θα τεθεί σε ERROR

κατάσταση.

Ο Καταχωρητής Διεύθυνσης Πλαισίου (Frame Address Register - FAR) κρατάει την διεύθυνση του

τρέχοντος πλαισίου. Η διεύθυνση χωρίζεται σε τρία μέρη : τον τύπο μπλοκ, την μείζονα διεύθυνση και

την ελάσσονα διεύθυνση. Ο τύπος μπλοκ δείχνει αν χρησιμοποιείται ο CLB ή ο block RAM χώρος

διευθύνσεων. Η μείζων διεύθυνση επιλέγει την CLB ή RAM στήλη και η ελάσσων διεύθυνση επιλέγει το

πλαίσιο μέσα στην στήλη.

O Καταχωρητής Δεδομένων Πλαισίου Εισόδου (Frame Data Input Register - FDRI) χρησιμοποιείται για

να φορτώσει τα configuration δεδομένα σε μια Virtex συσκευή. Είναι ένας καταχωρητής ολίσθησης στον

οποίο φορτώνονται τα δεδομένα πριν μεταφερθούν στην configuration μνήμη. Για την διαδικασία της

εγγραφής χρησιμοποιείται ένα pipeline τέτοιο ώστε το πρώτο πλαίσιο δεδομένων να γράφεται στην

configuration μνήμη ενώ το δεύτερο πλαίσιο να ολισθαίνει μέσα. Το τελευταίο πλαίσιο (pad frame)

είναι πάντα «χαζά» (dummy) δεδομένα που δεν γράφονται στην πραγματικότητα στην configuration μνήμη. Κάθε

πλαίσιο πρέπει να περιλαμβάνει αρκετές λέξεις των 32-bit ώστε να φορτωθεί το πλαίσιο πλήρως. Για το

pipelining υλικό απαιτείται η τελευταία λέξη κάθε πλαισίου να είναι μηδενικά (pad word).

O Καταχωρητής Δεδομένων Πλαισίου Εξόδου (Frame Data Output Register - FDRI) χρησιμοποιείται για

την ανάγνωση configuration δεδομένων από την συσκευή. Η διαδικασία αυτή καλείται Readback.

Κοντά στην αρχή του configuration bitstream, στον Καταχωρητή Μήκους Πλαισίου (Frame Length

Register - FLR) γράφεται το μήκος ενός πλαισίου, μετρημένο σε λέξεις των 32-bits. Ο αριθμός αυτός

γράφεται για να παρέχει πληροφορία για τον χρονισμό των λειτουργιών εγγραφής και ανάγνωσης.

Ο Καταχωρητής Μάσκας (Mask Register - MASK) χρησιμοποιείται σαν μάσκα για τις εγγραφές στον

καταχωρητή CTL. Ένα "1" στο bit στην θέση N της μάσκας επιτρέπει αυτή η θέση να γραφεί στον

καταχωρητή CTL.

O Καταχωρητής Ελέγχου (Control Register - CTL) καθοριζει το επίπεδο ασφαλείας της συσκευής και το

αν θα διατηρηθεί το configuration interface μετά το configuration. Η ασφάλεια της συσκευής

σχετίζεται με το αν επιτρέπεται μετά το αρχικό configuration να διαβαστούν τα configuration δεδομένα

καθώς επίσης και αν επιτρέπεται να αλλαχθεί το configuration. Όσον αφορά το configuration interface,

αν αυτό διατηρηθεί σημαίνει ότι οι ακροδέκτες που σχετίζονται με το configuration αλλά δεν είναι

αφιερωμένοι αποκλειστικά σε αυτό, θα διατηρήσουν την ιδιότητα τους και μετά το configuration.

Δίνεται έτσι η δυνατότητα επαναπρογραμματισμού της συσκευής κατά την διάρκεια λειτουργίας της.

Τέλος, ο Καταχωρητής Κατάστασης (Status Register - STAT) φορτώνεται με τις τιμές διάφορων σημάτων

κατάστασης ή ελέγχου.

Configuration Interfaces

Η σειρά Virtex υποστηρίζει τέσσερα configuration interfaces :

- Slave - Serial

- Master - Serial

- SelectMAP

- Boundary - Scan

Για τον καθορισμό του interface που θα χρησιμοποιηθεί για το configuration της συσκευής,

υπάρχουν τρεις ειδικοί ακροδέκτες (Μ2, Μ1, Μ0). Οι τιμές τους καθορίζουν όχι μόνο το configuration

mode αλλά και το κατά πόσο οι IOB ακροδέκτες θα είναι pulled - up ή floating πριν το configuration.

Ο Πίνακας 3 δείχνει τις διαφορετικές επιλογές που μπορούν να γίνουν.

Πίνακας 3. Configuration Κώδικες

| Configuration Mode |

Μ2 |

M1 |

M0 |

Κατεύθυνση CCLK |

Πλάτος Δεδομένων |

Configuration Pull-ups |

| Master-Serial Mode |

0 |

0 |

0 |

Out |

1 |

Όχι |

| Boundary-Scam Mode |

1 |

0 |

1 |

N/A |

1 |

Όχι |

| SelectMAP Mode |

1 |

1 |

0 |

In |

8 |

Όχι |

| Slave-Serial Mode |

1 |

1 |

1 |

In |

1 |

Όχι |

| Master-Serial Mode |

1 |

0 |

0 |

Out |

1 |

Ναι |

| Boundary-Scam Mode |

0 |

0 |

1 |

N/A |

1 |

Ναι |

| SelectMAP Mode |

0 |

1 |

0 |

In |

8 |

Ναι |

| Slave-Serial Mode |

0 |

1 |

1 |

In |

1 |

Ναι |

Ανεξάρτητα από το configuration mode που επιλέγεται, το configuration μέσω του Boundary-scan port

είναι πάντα διαθέσιμο. Αν επιλεγεί αυτό, τότε απλά απενεργοποιούνται τα άλλα modes.

Για την υλοποίηση των διαφόρων configuration interfaces οι συσκευές Virtex διαθέτουν έναν αριθμό

ακροδεκτών, από τους οποίους άλλοι χρησιμοποιούνται αποκλειστικά για τον σκοπό αυτό και άλλοι μετά

το πέρας της διαδικασίας μπορούν να χρησιμοποιηθούν από τον χρήστη. Από τους ακροδέκτες που

χρησιμοποιούνται αποκλειστικά για τον σκοπό αυτό, έχουν ήδη αναφερθεί οι M2, M1 και Μ0. Πέραν αυτών,

υπάρχουν τρεις ακόμα : ο ακροδέκτης CCLK, ο οποίος χρησιμοποιείται για την παροχή του ρολογιού που

χρονίζει την διαδικασία του configuration, ο ακροδέκτης PROGRAM που χρησιμοποιείται στην έναρξη της

διαδικασίας για να «καθαρίσει» την εσωτερική configuration μνήμη και ο ακροδέκτης DONE που

χρησιμοποιείται για να σηματοδοτήσει το τέλος της διαδικασίας. Στους ακροδέκτες αυτούς πρέπει να

συνυπολογιστούν και οι τέσσερις ακροδέκτες που σχετίζονται με το Boundary-Scan (TDI, TDO, TMS, TCK).

Στη συνέχεια παρουσιάζεται κάθε configuration interface ξεχωριστά. Έμφαση δίνεται μόνο στο

SelectMAP interface που αναλύεται διεξοδικά. Η σύντομη αναφορά στα άλλα διαθέσιμα interfaces γίνεται

για λόγους πληρότητας.

Slave-Serial Mode

Όταν το configuration γίνεται σε slave-serial mode, το FPGA λαμβάνει την configuration πληροφορία

σε σειριακή bit προς bit μορφή από μια σειριακή PROM ή κάποια άλλη πηγή σειριακών configuration

δεδομένων. Για την είσοδο των δεδομένων χρησιμοποιείται ο ακροδέκτης DIN, ο οποίος μετά την

ολοκλήρωση του configuration μπορεί να χρησιμοποιηθεί από τον χρήστη. Ένας δεύτερος ακροδέκτης

(DOUT) χρησιμοποιείται σε αυτό το interface για να προωθεί την configuration πληροφορία προς άλλα

FPGA όταν αυτά έχουν συνδεθεί σε αλυσίδα.

Στο interface αυτό, το ρολόι για το configuration παρέχεται από μια εξωτερική πηγή. Η μέγιστη

συχνότητα που επιτρέπεται να έχει είναι 66 ΜΗz.

Master-Serial Mode

Σε αντίθεση με το προηγούμενο mode, ο ακροδέκτης CCLK του FPGA λειτουργεί ως έξοδος και παρέχει

το ρολόι που οδηγεί μια σειριακή PROM. H PROM αυτή τροφοδοτεί με σειριακά δεδομένα την DIN είσοδο

του FPGA. Ένας εσωτερικός ταλαντωτής αναλαμβάνει να παράγει το ρολόι, η συχνότητα του οποίου όπως

και στο slave-serial mode μπορεί να είναι 66 MHz μέγιστο. Η συχνότητα που θα έχει καθορίζεται από

συγκεκριμένη παράμετρο που περιέχεται στο configuration bitstream. Κατά τα άλλα λειτουργεί με

ακριβώς όμοιο τρόπο με το slave-serial mode.

Boundary-Scan Mode

Στο mode αυτό, το configuration γίνεται μέσω του IEEE 1149.1 Τest Access Port. Είναι και αυτό

σειριακό mode, όπως και τα προηγούμενα δύο, αλλά κατά τα άλλα δεν παρουσιάζει άλλες ομοιότητες.

Είναι αρκετά διαφορετικό χρησιμοποιώντας διαφορετικούς ακροδέκτες και καταχωρητές. Έτσι πρέπει να

εισαχθούν πρώτα οι κατάλληλες εντολές στους ειδικούς καταχωρητές του Boundary-Scan και μετά να

εισαχθεί το configuration bitstream.

SelectMAP Mode

To SelectMAP είναι το mode εκείνο που προσφέρεται για το ταχύτερο configuration. Τα configuration

δεδομένα γράφονται ανά bytes στο FPGA και υπάρχει μια σημαία BUSY για τον έλεγχο της ροής τους.

Μια εξωτερική πηγή δεδομένων παρέχει ένα byte stream, το CCLK, ένα σήμα Επιλογής Ολοκληρωμένου

(Chip Select - CS) αρνητικής λογικής και ένα σήμα εγγραφής (WRITE - επίσης αρνητικής λογικής). Εάν

κατά το configuration το σήμα BUSY ενεργοποιηθεί από το FPGA, τότε τα δεδομένα πρέπει να κρατηθούν

μέχρι να απενεργοποιηθεί.

Το ρολόι CCLΚ μπορεί να έχει μέγιστη συχνότητα μέχρι 66 MHz. Μπορεί να παρέχεται είτε από ένα

εξωτερικό κύκλωμα είτε από έναν ελεύθερο ταλαντωτή. Για συχνότητες μέχρι και 50 MHz το σήμα BUSY

μπορεί να αγνοηθεί.

Για να εισαχθούν τα δεδομένα στο FPGA, χρησιμοποιούνται 8 ακροδέκτες (D0 μέχρι D7). Οι ακροδέκτες

αυτοί μετά την ολοκλήρωση του configuration μπορούν να χρησιμοποιηθούν από τον χρήστη. Παρόλα αυτά

επειδή το SelectMAP μπορεί να χρησιμοποιηθεί για τον επαναπρογραμματισμό της συσκευής ή για την

ανάγνωση των configuration δεδομένων της, εάν καθορίζεται από το bitstream οι ακροδέκτες αυτοί

μπορούν να διατηρήρουν την ιδιότητα τους και μετά την ολοκλήρωση του configuration. Να σημειωθεί

τέλος ότι ο ακροδέκτης D0 ταυτίζεται με τον ακροδέκτη DIN που αναφέρθηκε στα modes slave-serial και

master-serial.

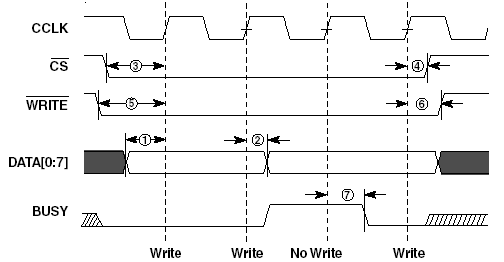

Σε μια λειτουργία εγγραφής στέλνονται πακέτα configuration πληροφορίας στο FPGA. Η σειρά των

λειτουργιών περιγράφεται ακολούθως :

- Μετάβαση των /WRITE και /CS σημάτων σε Low. Αν το /CS κατεβαίνει σε συνεχόμενους κύκλους, τότε

το /WRITE πρέπει να παραμείνει ή ενεργοποιημένο ή απενεργοποιημένο.

- Oδήγηση δεδομένων στους ακροδέκτες D[0:7]. Για να αποφευχθεί οποιαδήποτε σύγκρουση η πηγή των δεδομένων πρέπει να μην ενεργοποιείται όσο το /CS είναι Low και το /WRITE High. Όμοια, αν το /WRITE είναι High, δεν πρέπει να εισαχθούν περισσότερα του ενός /CS.

- Αν στην ανερχόμενη ακμή του CCLK το σήμα BUSY είναι Low, τότε τα δεδομένα γίνονται δεκτά σε αυτόν τον κύκλο ρολογιού. Διαφορετικά, απορρίπτονται. Η αποδοχή των δεδομένων θα γίνει στο πρώτο κύκλο ρολογιού μετά την μετάβαση του BUSY από High σε Low. Όσο το BUSY είναι High, τα δεδομένα πρέπει να κρατηθούν. Να σημειωθεί στο σημείο αυτό ότι αν το CCLK είναι μικρότερο από 50 MHz, το FPGA δεν πρόκειται να σηκώσει ποτέ το BUSY, οπότε η διαδικασία αυτή μπορεί να αγνοηθεί.

- Επανάληψη των βημάτων 2 και 3 μέχρι να σταλεί όλη η configuration πληροφορία.

- Απενεργοποίηση των σημάτων /CS και /WRITE.

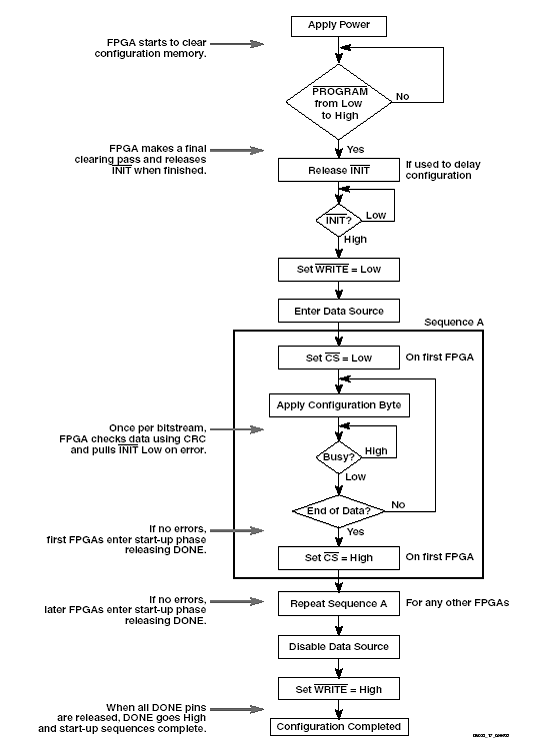

To Σχήμα 13 δίνει το διάγραμμα χρονισμού της διαδικασίας αυτής. Στο Σχήμα 14 παρατίθεται το

σχετικό διάγραμμα ροής.

Σχήμα 13. Λειτουργίες Εγγραφής

Σχήμα 14. Διάγραμμα Ροής για SelectMAP Λειτουργίες Εγγραφής

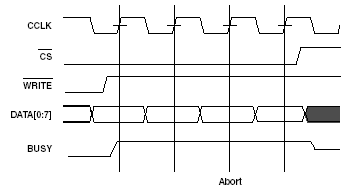

Κατά την διάρκεια μιας ενεργοποίησης του /CS, ο χρήστης δεν μπορεί να μεταβεί από μια λειτουργία

εγγραφής σε μια λειτουργία ανάγνωσης και το αντίστροφο. Κάτι τέτοιο θα προκαλέσει την απόρριψη της

εντολής του τρέχοντος πακέτου. Η συσκευή θα παραμείνει BUSY μέχρι να ολοκληρωθεί η απορριφθείσα

εντολή. Στη συνέχεια, τα δεδομένα θεωρούνται ότι έχουν χάσει την στοίχιση τους σε σχέση με τα όρια

των λέξεων και έτσι το FPGA απαιτεί την αποστολή μιας νέας λέξης συγχρονισμού πριν να μπορέσει να

δεχτεί νέα πακέτα.

Για να ξεκινήσει μια διαδικασία απόρριψης (abort) κατά την διάρκεια μιας λειτουργίας εγγραφής,

πρέπει να απενεργοποιηθεί το σήμα /WRITE. Στην θετική ακμή του CCLK, η διαδικασία απόρριψης θα

ξεκινήσει (Σχήμα 15).

Σχήμα 15. Διάγραμμα Χρονισμού μιας SelectMAP Απόρριψης Εγγραφής

Όπως φαίνεται και από διάγραμμα ροής που παρατίθεται (Σχήμα 14) το configuration μιας Virtex

συσκευής είναι μια διαδικασία τριών σταδίων. Στο πρώτο στάδιο, η configuration μνήμη της συσκευής

«καθαρίζεται». Στο δεύτερο στάδιο φορτώνονται τα configuration δεδομένα στην μνήμη και τέλος η λογική

ενεργοποιείται μέσω μιας διαδικασίας εκκίνησης.

Η διαδικασία του configuration ξεκινά αυτόματα με την ενεργοποίηση (power-up) της συσκευής. Υπάρχει

η δυνατότητα ο χρήστης να καθυστερήσει την εκκίνησης της. Αυτό μπορεί να γίνει αν το σήμα /INIT

κρατηθεί σε Low με χρήση ενός οδηγού ανοικτού - συλλέκτη. Όση ώρα παραμένει το σήμα σε αυτήν την

κατάσταση η configuration διαδικασία τίθεται σε αναμονή. Αν το σήμα /PROGRAM ενεργοποιηθεί, ο χρήστης

μπορεί να προκαλέσει επανεκκίνηση της configuration διαδικασίας.

Το τέλος της φάσης καθαρισμού της μνήμης σηματοδοτείται από την μετάβαση του σήματος /INIT σε High.

Η ολοκλήρωση του configuration σηματοδοτείται από την μετάβαση του DONE σε High.

H διαδικασία εκκίνησης του ολοκληρωμένου (start-up) ξεκινά ένα CCLK κύκλο μετά την μετάβαση του

DONE σε High. Τότε ενεργοποιείται το καθολικό σήμα τριών καταστάσεων GTS. Αυτό θα επιτρέψει σε όλες

τις εξόδους τις συσκευής να μεταβούν στην κατάλληλη κατάσταση. Ένα κύκλο αργότερα, ενεργοποιούνται τα

Global Set/Reset (GSR) και Global Write Enable (GWE) σήματα. Αυτά θα επιτρέψουν στα εσωτερικά

αποθηκευτικά στοιχεία να αρχίσουν να αλλάζουν καταστάσεις σύμφωνα με τις επιταγές της εσωτερικής

λογικής και του ρολογιού του χρήστη.

Partial Reconfiguration

H οικογένεια ολοκληρωμένων Virtex υποστηρίζει την δυνατότητα να επαναπρογραμματιστεί ένα μέρος της

συσκευής κατά την διάρκεια της λειτουργίας της. Εάν κατά την διάρκεια του μερικού επαναπρογραμματισμού

(partial reconfiguration), το τμήμα της συσκευής που παραμένει σταθερό συνεχίζει να λειτουργεί, η

διαδικασία καλείται δυναμική (dynamic partial reconfiguration). Η αντίθετη περίπτωση (το σταθερό

τμήμα αναστέλει την λειτουργία του όσο διαρκεί ο επαναπρογραμματισμός) καλείται στατική.

Για το partial reconfiguration (είτε στατικό είτε δυναμικό) ισχύουν οι βασικές αρχές που έχουν

αναφερθεί προηγουμένως. Παρουσιάζονται όμως και ορισμένες διαφορές λόγω της ιδιομορφίας του.

Κατ'αρχήν δεν είναι διαθέσιμα όλα τα configuration interfaces για την διαδικασία αυτή. Μπορούν να

χρησιμοποιηθούν μόνο τα SelectMAP και Boundary-Scan.

To Boundary-Scan interface παραμένει ενεργό καθόλη την διάρκεια λειτουργίας της συσκευής σε

αντίθεση με το SelectMAP. Έτσι για να είναι εφικτό το partial reconfiguration με χρήση του SelectMAP

πρέπει να δηλωθεί στο αρχικό configuration bitstream ότι το interface αυτό θα διατηρηθεί και μετά το

πέρας του αρχικού προγραμματισμού. Αυτό συνεπάγεται ότι όλοι οι ακροδέκτες που σχετίζονται με το

SelectMAP δεν θα μπορούν να χρησιμοποιηθούν από τον χρήστη μετά το configuration.

Μια άλλη διαφορά σε σχέση με την διαδικασία του απλού configuration είναι ότι το σήμα /PROGRAM δεν

πρέπει να ενεργοποιηθεί κατά την έναρξη της διαδικασίας. Αυτό θα είχε ως αποτέλεσμα την διαγραφή όλης

της configuration πληροφορίας. Έτσι η ενεργοποίηση των σημάτων /CS και /WRITE είναι εκείνη που

σηματοδοτεί την αρχή του partial reconfiguration.

Επίσης, ενώ κατά το απλό configuration, το τέλος της διαδικασίας σηματοδοτείται από την μετάβαση

του DONE σε High, κάτι τέτοιο δεν ισχύει στην περίπτωση του partial reconfiguration. Για τούτο

συνίσταται η χρήση κάποιας εξωτερικής λογικής που θα τροφοδοτήσει το FPGA με τον ακριβή αριθμό

configuration δεδομένων.

Τέλος να σημειωθεί ότι αν το partial reconfiguration θα είναι στατικό ή δυναμικό καθορίζεται από

συγκεκριμένες επιλογές που ενσωματώνονται στο bitstream που περιέχει την partial reconfiguration

πληροφορία.

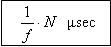

Όσον αφορά τον χρόνο που απαιτείται για ένα partial reconfiguration μιας Virtex συσκευής, αυτός

είναι ευθέως ανάλογος του μήκους του partial bitstream και αντιστρόφος ανάλογος της συχνότητας με την

οποία χρονίζεται το configuration interface που χρησιμοποιείται. Για παράδειγμα, αν χρησιμοποιηθεί το

SelectMAP interface χρονισμένο στα f MHz και το partial bitstream έχει μήκος Ν bytes, τότε ο χρόνος

που απαιτείται είναι :

ΠΗΓΕΣ.

1. Xilinx Inc., 'Virtex 2.5V Field Programmable Gate Arrays - Product Specification (DS003-1 v.2.5)', April 2, 2001

2. Xilinx Inc., 'VirtexT 2.5V Field Programmable Gate Arrays - Production Product Specification (DS003-3 v.3.2)', September 10, 2002

3. Xilinx Inc., 'Application Note 151 : Virtex Series Configuration Architecture User Guide', March 24, 2003

4. Xilinx Inc., 'Application Note 138 : Virtex FPGA Series Configuration and Readback', July 11, 2002

|